Troche teorii..

W drugiej fazie przekształcania adresu logicznego na adres fizyczny, procesor transformuje adres liniowy w adres fizyczny. W fazie tej występują podstawowe mechanizmy, które umożliwiają zaimplementowanie procedur mechanizmu pamięci wirtualnej opartej na wymianie stron, jak również ochronę pamięci na poziomie stron.

Translacja stronicowania jest funkcją opcjonalną i występuje tylko wtedy, gdy jest ustawiony bit PG w rejestrze kontrolnym CR0. Jeśli flaga PG ma wartość zero to adres liniowy staje się automatycznie adresem fizycznym. Bit PG jest zazwyczaj ustawiany przez system operacyjny w trakcie inicjowania systemu. Stronicowanie musi być włączone jeśli chcemy skorzystać z trybu pracy wirtualnej procesora.

Mechanizm stronicowania dzieli pamięć na 4KB strony - ciągłe, niepodzielne przestrzenie adresowe pamięci fizycznej o stałej wielkości.

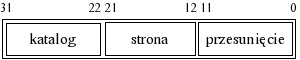

Adres liniowy

Adres liniowy odnosi się pośrednio do pamięci fizycznej poprzez określenie tablicy stron w katalogu, odpowiedniej strony w tej tablicy stron, oraz przesunięcia wewnątrz tej strony.

|

| Rys. Adres liniowy |

Mechanizm stronicowania procesora Intel386 stosuje dwupoziomową tablicę stron. Na wyższym poziomie znajduje się katalog stron (ang. page directory), który zawiera do 1024 wpisów tablic stron drugiego poziomu. Na poziomie niższym znajduje się tablica stron (ang. page table), która może zawierać do 1024 wpisów stron. Wszystkie tablice stron są adresowane poprzez jeden katalog stron. W sumie można zaadresować 2^20 stron. Ponieważ każda ze stron ma wielkość 4KB, struktura ta może zaadresować całą przestrzeń adresową procesora: 2^(20)*2^(12)=2^(32).

Adres fizyczny aktualnego katalogu stron przechowywany jest w rejestrze CR3, zwanym również rejestrem bazowym katalogu stron (ang. page directory base register - PDBR). Procedura zarządzania pamięcią w systemie operacyjnym ma możliwość używania jednego katalogu stron dla wszystkich zadań, jednego katalogu dla każdego zadania, lub obu kombinacji naraz.

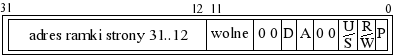

Wpis do talbic

Wpis do tablic obu poziomów ma ten sam format:

|

| Rys. Format wpis do tablicy stron |

Opis pól wpisu do tablic stron:

- Adres ramki strony - wartość ta określa fizyczny adres strony. Ponieważ granice adresów stron są co 4KB, 12 mniej znaczących bitów ma zawsze wartość zero - mogą być wykorzystane do innych celów. W katalogu stron adres ramki jest adresem tablicy stron, w tablicy stron adres ramki jest adresem strony która zawiera potrzebną komórkę pamięci.

- P - bit 'obecności' - bit ten wskazuje czy wpis ten może być wykorzystany w translacji adresów.

- Kiedy P = 0 wpis jest nie wykorzystywany przez procesor: żaden z pozostałych bitów nie jest sprawdzany przez procesor. Wpis może być więc dostępny dla projektanta systemu. Podczas próby dostępu do komórki pamięci poprzez taki wpis procesor sygnalizuje wyjątek strony (ang. page exception). W systemach z pamięcią wirtualną opartą na wymianie stron wyjątek ten może być sygnałem braku strony w pamięci operacyjnej i wywoływać odpowiednią podprocedure mechanizmu wymiany stron. Instrukcja, która wywołała wyjątek może być następnie ponownie wywołana.

- Kiedy P = 1 wpis może być wykorzystany do translacji adresów

- A - bit dostępu - bit ten wskazuje czy dana strona była używana. Procesor ustawia ten bit jeśli wykonywał operacje odczytu lub zapisu w danej stronie. Bit ten nie jest zerowany przez procesor.

- D - bit 'zabrudzenia' - bit ten oznacza, że dane na stronie zostały zmienione. Procesor ustawia ten bit we wpisie strony w tablicy stron przed operacją zapisu pod żądany adres. Bit ten jest nieokreślony w katalogu stron.

- R/W i U/S - bity te nie mają wpływu na mechanizm translacje adresów; są używane przez mechanizm ochrony zasobów.

System operacyjny obsługujący pamięć wirtualną może używać bitów D i A w celu określenia, które ze stron należy przenieść do pamięci tymczasowej, gdy obszar wymagany przez aplikacje przekracza wielkość fizyczną pamięci. Mechanizm stronicowania system operacyjnego jest zobligowany do sprawdzania i właściwego zerowania tych bitów.

|

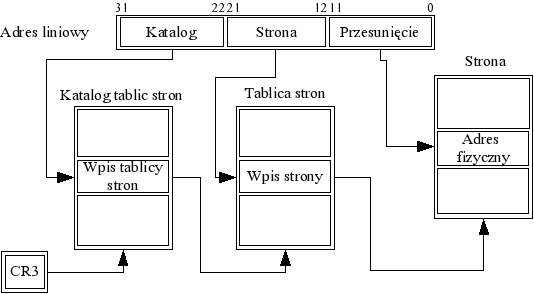

| Rys. Translacja segmentacji |

Proces translacji adresu liniowego na adres fizyczny przebiega w sposób następujący: adres katalogu tablic stron znajduje się w rejestrze CR3; procesor według obszaru 'Katalog' w adresie liniowym pobiera z katalogu tablic stron odpowiedni wpis dotyczący tablicy stron. W wpisie tym znajduje się fizyczny, bazowy adres tablicy stron. Z danej tablicy stron procesor pobiera wpis określony obszarem 'Strona' w adresie liniowym. W tym wpisie znajduje się fizyczny, bazowy adres żądanej strony pamięci. Interesujący nas adres znajduje się w otrzymanej stronie pamięci pod przesunięciem o wartości umieszczonej w obszarze 'Przesunięcie' w adresie liniowym.

Pobranie odpowiedniego wpisu z tablicy stron/katalogu stron jest to po prostu dodanie do adresu bazowego tablicy odpowiedniej wartości umieszczonej w adresie liniowym pomnożonej o wielkość wpisu strony (32 bity - 4 bajty).

Pamięć podręczna translacji stronicowania

W celu zwiększenia wydajności procesor przechowuje najczęściej używane wpisy z tablicy stron w specjalnym buforze. Dzięki takiemu rozwiązaniu nie ma potrzeby za każdym razem odwoływać się do katalogu tablic stron i tablic stron - dzieje się tak tylko wówczas kiedy danego wpisu nie ma w buforze. Obecność pamięci podręcznej translacji stronicowania (ang. page-translation cache) jest niewidoczna dla aplikacji, istnieje jednak pewna nad nią kontrola z poziomu systemu operacyjnego. Opcja ta została zawarta dlatego, gdyż istnieje potrzeba wyczyszczenia tego bufora, gdy zostaną zmienione katalog tablic stron lub tablice. Istnieją dwie metody zerowania bufora: poprzez ponowne załadowanie rejestru CR3 adresem katalogu, lub też przez przełączenie zadania na takie, które posiada inną wartość rejestru CR3 w segmencie TSS.