Kontroler przerwań

Podczas współpracy procesora z urządzeniami zewnętrznymi istnieje potrzeba asynchronicznego powiadamiania o zdarzeniach, które wystąpiły w nieprzewidywalnym czasie. Przykładem takiego zdarzenia może być naciśnięcie klawisza klawiatury, zakończenie operacji wejścia/wyjścia z pamięci masowej itp. Bez odpowiedniego układu kontrolującego przerwania, procesor musiałby co jakiś interwał czasowy sprawdzać wszystkie urządzenia zewnętrzne (ang. pooling), czy nie wymagają obsługi. Takie rozwiązanie niesie ze sobą niepotrzebną stratę czasu procesora i powoduje, iż wiele urządzeń zewnętrznych wymagało by obszernych buforów na dane do komunikacji z procesorem, jak również bardziej rozbudowanych mechanizmów, które automatyzowały by w większym stopniu ich prace. To oczywiście podnosi koszty produkcji takiego urządzenia. Innym przykładem mogą być systemy czasu rzeczywistego, w których urządzenia zewnętrzne powinny być obsłużone w jak najkrótszym czasie (np. pomiary szybkozmiennych wielkości fizycznych w systemach krytycznych).

W celu wyeliminowania cech negatywnych mechanizmu przepytywania urządzeń zewnętrznych wprowadzono zewnętrzne, programowalne kontrolery przerwań współpracujące z typowymi procesorami. Przykładem takiego układu jest układ Intel8259A. Był on specjalnie zaprojektowany jako układ peryferyjny dla procesorów rodziny 8086/8088 i został wykorzystany w komputerze IBM XT.

Oryginalny komputer IBM-PC/XT, oparty na procesorze Intel8088 posiadał pojedynczy układ kontrolera przerwań i8259, który umożliwiał obsługę ośmiu linii przerwań (IRQ 0-7). Następny komputer osobisty firmy IBM - PC/AT z procesorem 80286 i lepszymi, posiadał już dwa układy kontroli przerwań połączone ze sobą w sposób kaskadowy.

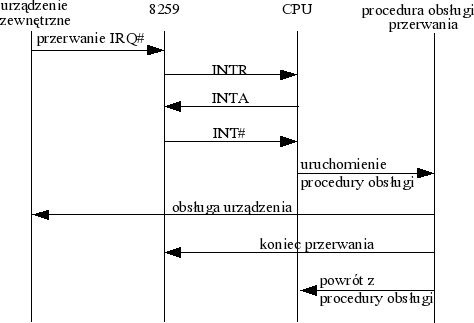

Procesory rodziny 80x86 posiadają tylko jedną linie żądania obsługi przerwania (INTR). Pomiędzy procesorem a układem kontrolera występuje transmisja charakteryzująca się prostym protokołem:

Protokół obsługi przerwań

|

| Rys. Protokół obsługi przerwania |

Kiedy urządzenie zewnętrzne generuje przerwanie, jest to zgłaszane układowi PIC. Żeby poinformować procesor o nadejściu przerwania, układ 8259 wysyła sygnał żądania obsługi przerwania INTR. Procesor w dogodnym dla siebie momencie odpowiada, że jest gotowy do obsługi przerwania, wysyłając do kontrolera sygnał INTA. W tym momencie kontroler przerwań wystawia 8-bitowy numer identyfikatora przerwania na szynę danych, co umożliwia procesorowi zorientowanie się, którą procedurę obsługi należy uruchomić. Po skończeniu obsługi przerwania procesor powiadamia o tym układ 8259 wysyłając sygnał końca przerwania (ang. end of interrupt - EOI) i zwraca sterowanie przerwanemu programowi.

Ponieważ istnieje prawdopodobieństwo wywołania więcej niż jednego przerwania w danym czasie, lub wywołania przerwania w chwili, kiedy już jest jakieś właśnie wykonywane, kontroler 8259 ma możliwość decydowania, które z przerwań ma najwyższy priorytet i powinno być wykonane jako pierwsze, jak również może zbuforować pozostałe, i poinformować o nich procesor, gdy ten zakończy obsługę przerwania z wyższym priorytetem.

W komputerach zgodnych z IBM-PC/AT występują dwa układy PIC, tak więc ma on możliwość obsługi piętnastu (IRQ-0 do IRQ-15) urządzeń zewnętrznych. Dla każdego przerwania sprzętowego musi zostać przydzielony identyfikator - liczba jaka będzie przedstawiana procesorowi w chwili potwierdzenia przerwania. Kontrolery umieszczone są w przestrzeni adresowej portów wejścia/wyjścia pod adresami 0x20 i 0x21 dla PIC1, oraz 0xA0 i 0xA1 dla PIC2.

Przydział identyfikatorów do przerwań sprzętowych powinien być wykonany przed użyciem mechanizmu przerwań, czyli praktycznie na początku inicjacji systemu.

Programowanie układu i8259A

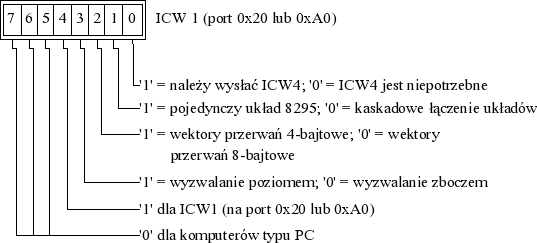

Procedura programowania układu i8259A składa się z następujących kroków:

- Zapis pierwszego słowa inicjującego (ang. initialization command word - ICW) ICW1 do portu 0x20 (lub 0xA0)

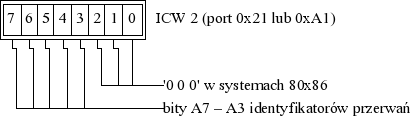

- zapis drugiego słowa słowa inicjującego ICW2 do portu 0x21 (lub 0xA1)

- jeśli bit D1 w ICW1 ma wartość zero zapisz słowo ICW3 do portu 0x20 (lub 0xA1)

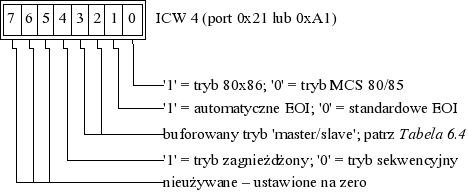

- zapis słowa inicjującego ICW4 do portu 0x21 (lub 0xA1)

- słowa kontrolne (ang. operation control word - OCW) mogą być teraz wysyłane w dowolnej kolejności

|

| Rys. Słowo inicjujące ICW1 |

|

| Rys. Słowo inicjujące ICW2 |

|

| Rys. Słowo inicjujące ICW4 |

Trzecie inicjujące słowo kontrolne ICW3 dla układu nadrzędnego określa numer przerwania przyznany dla układu podrzędnego w połączeniu kaskadowym kontrolerów. W przypadku układu podrzędnego trzy najmniej znaczące bity oznaczają identyfikator układu podrzędnego, pozostałe bity są ustawione na zero.

| Bit 3 | Bit 2 | Tryb buforowania |

| 0 | 0 | Bez buforowania |

| 0 | 1 | Bez buforowania |

| 1 | 0 | Buforowany układ podrzędny |

| 1 | 1 | Buforowany układ nadrzędny |

Słowo OCR1 jest to maska przerwań - umożliwia zablokowanie przyjmowania przerwania na poziomie kontrolera przerwań.