Układ zegara

Ponieważ, w systemach komputerowych, istnieje potrzeba odliczania stałych interwałów czasowych w sposób niesynchroniczny w stosunku do głównego zegara magistrali systemowej, wprowadzane są często oddzielne układy zegarowe synchronizowane za pomocą własnego zegara. W komputerach zgodnych z IBM-PC/AT rolę tę pełni układ, bądź para układów zgodnych z rodziną i8253/8254. Jego zadaniem jest przede wszystkim obsługa zegara systemowego czasu, wyznaczanie momentów w których ma odbyć się operacja odświeżania pamięci RAM, oraz kontrola nad systemowym generatorem tonów. W komputerach AT najczęściej wbudowany jest układ i8254 taktowany zegarem 10Mhz, w pełni zachowujący zgodność z układem i8253, który mógł być taktowany zegarem maksymalnie 2,6 Mhz. Układy te często nazywane są programowalnymi układami czasowo - licznikowymi (ang. programmable interval timer).

PIT zawiera trzy, niezależne od siebie 16-bitowe, liczące wstecz liczniki, wyposażone we własne wejścia CLOCK, GATE i wyjścia OUT. Każdy kanał posiada również 16-bitowy rejestr COUNT w którym przechowuje zliczoną wartość i rejestr CONTROL do nadzorowania działania licznika. W komputerze PC-AT licznik 0 stosowany jest do generowania przerwania IRQ 0, wykorzystywanego do obsługi zegara systemowego, licznik 1 obsługuje odświeżanie pamięci RAM, natomiast licznik 2 odpowiedzialny jest za generowanie tonu i może być, w przeciwieństwie do poprzednich, stosowany też w innych celach.

Każdy kanał układu pracować w jednym z sześciu trybów pracy:

- Tryb 0 (ang. interrupt on terminal count) - po załadowaniu licznika wyjście OUT jest zerowane i uruchamia się odliczanie licznika do 0, potem wyjście OUT osiąga wartość '1' i utrzymuje się ona do kolejnego wyznaczenia trybu pracy licznika.

- Tryb 1 (ang. programable one - shot) - po załadowaniu licznika wyjście OUT, które miało wartość 1, jest zerowane i rozpoczyna się odliczanie do 0, gdy je osiągnie wyjście OUT jest ustawiane na 1. Ten tryb powoduje wygenerowanie pojedynczego impulsu niskiego poziomu logicznego 0 o czasie trwania N*T(CLK).

- ryb 2 (ang. rate generator) - po załadowaniu licznika wyjście OUT, które miało wartość 1, jest zerowane i rozpoczyna się odliczanie do wartości 1, gdy je osiągnie wyjście OUT jest ustawiane na 1 na przeciąg jednego okresu . Po osiągnięciu zera wyjście OUT jest zerowane, a sam licznik jest ładowany ponownie wartością początkową N i cykl się powtarza. Generowany wykres szpilkowy o okresie N*T(CLK). Standardowo pracuje w nim licznik 1.

- Tryb 3 (ang. square wave mode) - po załadowaniu licznika wyjście OUT jest ustawiane na 1 i rozpoczyna się odliczanie do N/2, gdy je osiągnie wyjście OUT jest zerowane i następuje dalsze odliczanie do zera. Potem licznik jest ładowany ponownie wartością początkową N i cykl się powtarza. Generowany jest wykres prostokątny o współczynniku wypełnienia 1/2 gdy N parzyste, a gdy N jest nieparzyste następuje nieznaczna przewaga fazy wysokiego poziomu logicznego, ponieważ licznik CE jest ładowany wartością N-1.

- Tryb 4 (ang. software triggered strobe) - pierwszy impuls do rejestru sterującego uruchamia odliczanie, OUT jest ustawiona na 1, gdy licznik osiągnie wartość zero, OUT jest zerowane na okres T(CLK). Jest to programowe wyzwolenie licznika.

- Tryb 5 (ang. hardware triggered strobe / retriggerable) - licznik jest wyzwalany przez podanie jedynki na wejściu GATE, OUT jest ustawiona na jeden. Po N+1 cyklach jest podawany impuls 0 na wyjściu OUT. Ponowny impuls na GATE w czasie odliczania powoduje jego restart. Jest to sprzętowe wyzwolenie licznika.

Rejestr sterujący

|

| Rys. Rejestr sterujący układu 8253 |

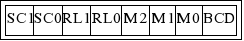

Rejestr sterujący układu 8253, w komputerach PC-AT znajduję sie przestrzeni adresowej portów wejścia/wyjścia procesora pod adresem 0x40 - 0x43. Jest to rejestr tylko do zapisu. Wybór kanału dokonuje się ustawiając bity SC0 i SC1. Jeśli oba bity wyboru są ustawione, to układ zostaje zablokowany. Zdefiniowanie trybu pracy odbywa się przy pomocy bitów M0 - M2. Bit BCD określa czy licznik ma pracować jako licznik binarny (stan niski), czy też licznik kodu BCD (stan wysoki). Bity Rlx określają operację jaka będzie przeprowadzona.

| M2 | M1 | M0 | Tryb Pracy |

Układ posiada cztery porty 8-bitowe ułożone w kolejności:

- 0x40 (0x48) - licznik generatora 0

- 0x41 (0x49) - licznik generatora 1

- 0x42 (0x4A) - licznik generatora 2

- 0x43 (0x4B) - rejestr sterujący (ang. control word register)

Programowanie

W celu zaprogramowania licznika należy najpierw wpisać konfiguracje do rejestru sterującego. Aby uniknąć zakłóceń zaleca się ustawienie parametrów pracy wszystkich kanałów, bez względu ile z nich wykorzystujemy. Jeśli potrzebujemy 16-bitowego licznika, to zazwyczaj powinniśmy zacząć od wprowadzenia bitu LSB, a następnie MSB. Dlatego wcześniej dla RL1 oraz RL0 w rejestrze kontroli należy wpisać wartość 1. Po dwukrotnym zapisaniu stan licznika zostaje ustalony. Rejestr licznika wypełniony zostanie dopiero wtedy, kiedy na wejściu taktowania pojawi się impuls.

Najwyższa wartość pracy licznika w trybie binarnym wynosi 65536, a dla trybu dziesiętnego 10000. Wielkość ta redukowana jest przy każdym impulsie taktowania.

Odczyt stanu licznika odbywa się w następujący sposób:

- w trybach 0, 2, 3, 4 - przez ustalenie wartości Low na wejściu GATE. Dzięki temu zachowany zostaje stan licznika, po czym można go odczytać. Podczas pierwszego czytania następuje odczyt LSB, podczas drugiego - MSB.

- RL0 oraz RL1 przyporządkowana jest w rejestrze kontroli wartość Low, następnie zostaje zachowany stan licznika, który potem można odczytać.

- Stan licznika można również odczytać dzięki tymczasowemu wprowadzeniu jego aktualnej wartości. Po zapisie specjalnego polecenia w rejestrze statusu, stan licznika zostaje tymczasowo zapisany, po czym gotowy jest do odczytu.

Aby odczytać stan licznika, należy wysłać komendę odczytu do rejestru sterującego. Komenda ta składa się z zer na wszystkich miejscach, oprócz bitów SCx, w których ustawiamy, który licznik nas interesuje.